|

#2

30th January 2017, 09:59 AM

| |||

| |||

| Re: UPPCL Mock Test

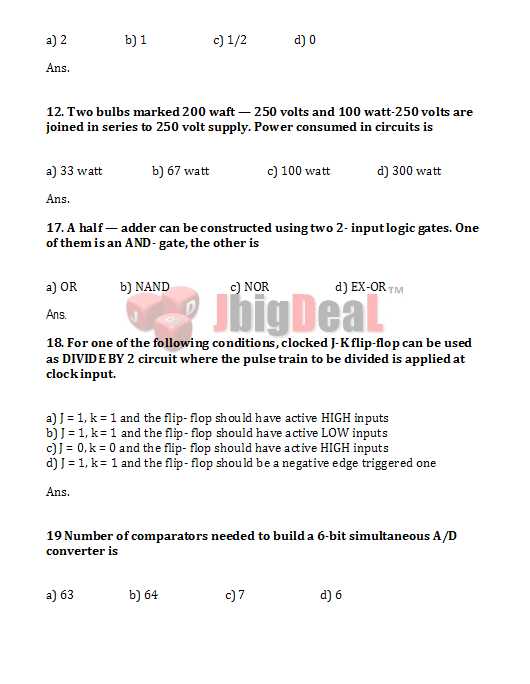

As you want mock test / sample papers of Junior Engineer Recruitment of UPPCL, so here I am providing following: UPPCL Junior Engineer Sample Paper of Electronics A differential amplifier has a differential gain of 20,000. CMRR = 80 dB. The common mode gain is given by a) 2 b) 1 c) 1/2 d) 0 Two bulbs marked 200 waft — 250 volts and 100 watt-250 volts are joined in series to 250 volt supply. Power consumed in circuits is a) 33 watt b) 67 watt c) 100 watt d) 300 watt A half — adder can be constructed using two 2- input logic gates. One of them is an AND- gate, the other is a) OR b) NAND c) NOR d) EX-OR For one of the following conditions, clocked J-K flip-flop can be used as DIVIDE BY 2 circuit where the pulse train to be divided is applied at clock input. a) J = 1, k = 1 and the flip- flop should have active HIGH inputs b) J = 1, k = 1 and the flip- flop should have active LOW inputs c) J = 0, k = 0 and the flip- flop should have active HIGH inputs d) J = 1, k = 1 and the flip- flop should be a negative edge triggered one Number of comparators needed to build a 6-bit simultaneous A/D converter is a) 63 b) 64 c) 7 d) 6 The AID converter used in a digital voltmeter could be (1) successive approximation type (2) Flash converter type (3) Dual slope converter type. The correct sequence in the increasing order of their conversion time taken is a) 1, 2, 3 b) 2, 1, 3 c) 3, 2, 1 d) 3, 1, 2 Which of the following binary number is equal to octal number 66.3 a) 101101.100 b) 1101111.111 C) 111111.1111 d) 110110.011 A 4-bit presetable UP counter has preset input 0101. The preset operation takes place as soon as the counter reaches 1111. The modulus of the counter is a) 5 b) 10 c) 11 d) 15 A 4-bit synchronous counter uses flip-flops with propagation delay time of 25 ns each. The maximum possible time required for change of state will be a) 25 ns b) 50 ns c) 75 ns d) 100 ns If a counter having 10 FFs is initially at 0, what count will if hold after 2060 Pulses a) 000 000 1100 b) 000 001 1100 c) 000 001 1000 d) 000 000 1110   To download full question paper, download the attachment..... |