|

#2

18th September 2014, 11:51 AM

| |||

| |||

| Re: Sample paper for GATE EEE Stream

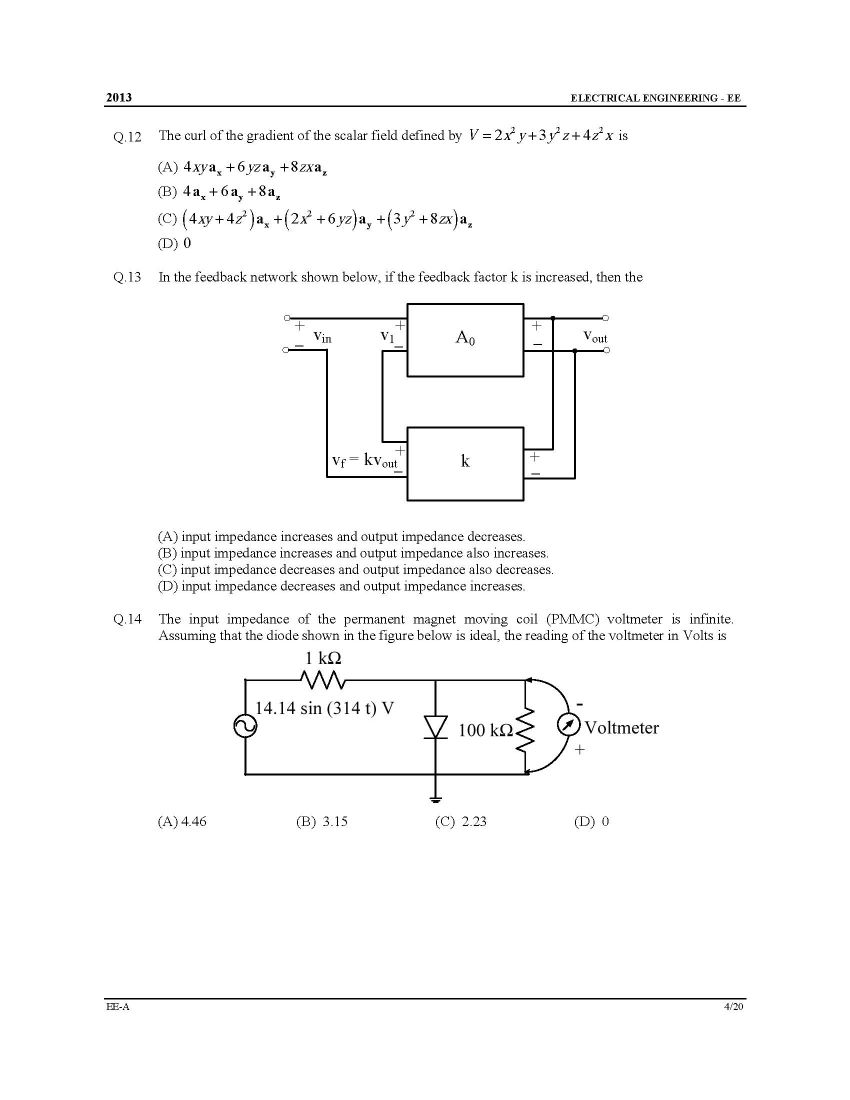

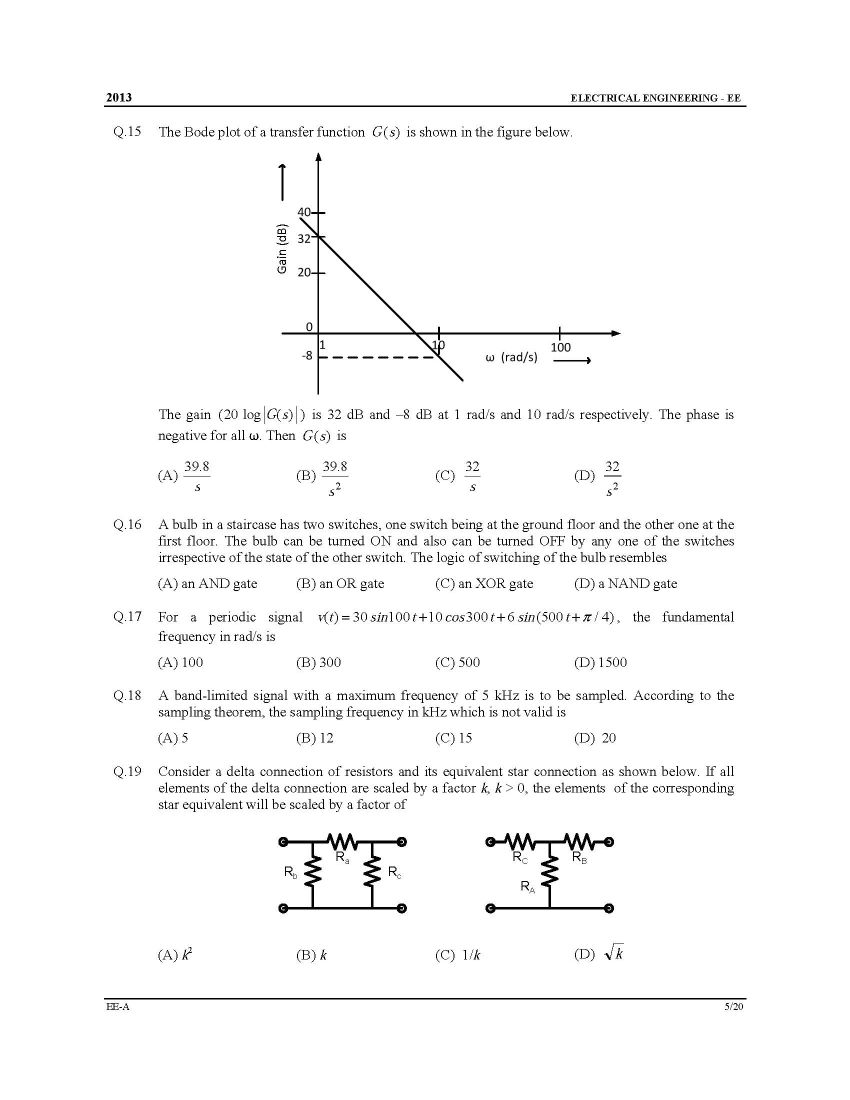

You are looking for GATE Electrical Engineering model question paper, I am giving here: A single-phase load is supplied by a single-phase voltage source. If the current flowing from the load to the source is 0 10 150 Ð- A and if the voltage at the load terminals is 0 100 60 Ð V, then the (A) load absorbs real power and delivers reactive power. (B) load absorbs real power and absorbs reactive power. (C) load delivers real power and delivers reactive power. (D) load delivers real power and absorbs reactive power. A single-phase transformer has no-load loss of 64 W, as obtained from an open-circuit test. When a short-circuit test is performed on it with 90% of the rated currents flowing in its both LV and HV windings, the measured loss is 81 W. The transformer has maximum efficiency when operated at (A) 50.0% of the rated current. (B) 64.0% of the rated current. (C) 80.0% of the rated current. (D) 88.8% of the rated current. In the feedback network shown below, if the feedback factor k is increased, then the (A) input impedance increases and output impedance decreases. (B) input impedance increases and output impedance also increases. (C) input impedance decreases and output impedance also decreases. (D) input impedance decreases and output impedance increases. A bulb in a staircase has two switches, one switch being at the ground floor and the other one at the first floor. The bulb can be turned ON and also can be turned OFF by any one of the switches irrespective of the state of the other switch. The logic of switching of the bulb resembles (A) an AND gate (B) an OR gate (C) an XOR gate (D) a NAND gate A band-limited signal with a maximum frequency of 5 kHz is to be sampled. According to the sampling theorem, the sampling frequency in kHz which is not valid is (A) 5 (B) 12 (C) 15 (D) 20 For detailed paper here is attachment:      |